# STi4500 STi4510

# MPEG AUDIO DECODER

#### ADVANCE DATA

- SINGLE-CHIP ISO/IEC 11172-3 (LAYER I & II) DECODER

- DECODES IN SINGLE CHANNEL, DUAL CHANNEL, STEREO OR JOINT STEREO MODES

- SUPPORTS ALL MPEG BIT RATES AT 32, 44.1 & 48kHz, AND FREE FORMAT AT 32 & 48kHz SAMPLING RATES

- INPUT CAN BE EITHER PACKETS OR AUDIO STREAM

- BIT OR BYTE MODE COMPRESSED DATA INPUT, WITH BURST RATE TO 20 Mbit/s

- STEREO OUTPUT LEVEL CONTROL

- 16 OR 18-BIT PCM OUTPUT, I<sup>2</sup>S AND OTHER FORMATS

- 8-BIT MICROCONTROLLER INTERFACE

- SUPPORT FOR 1MBIT OF EXTERNAL DRAM FOR AT LEAST 1 SECOND OF SYNCHRONI-ZATION DELAY

- INCLUDES SYSTEM TIME CLOCK FOR HANDLING OF A/V SYNCHRONIZATION & PTS EXTRACTION FROM PACKETS

- AUTOMATIC ERROR CONCEALMENT ON CRC OR SYNCHRONIZATION ERROR DE-TECTION

- LOW-POWER 5V CMOS TECHNOLOGY

- PRIMARY CLOCK FREQUENCY UP TO 28MHz

#### APPLICATIONS

- MULTIMEDIA COMPUTER

- VIDEO CD PLAYER

- DIGITAL TV RECEIVER

## DESCRIPTION

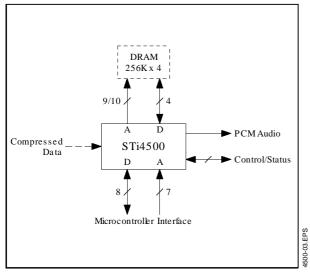

The STi4500 is a single-chip audio decompression processor compliant with layers 1 and 2 of the ISO/IEC 11172-3 (MPEG) standard. Input data is accepted at any of the MPEG-defined data rates, and PCM output is provided at 32, 44.1 or 48kHz sampling rates.

The input data may be in the form of packets or an audio elementary stream. In the former case the STi4500 extracts the audio packet data. The input rate can be either constant or in bursts up to 20 Mbit/s. Data can be input either in bytes through the microcontroller interface or through a dedicated serial port.

The PCM audio output, selectable to be either 16 bits or 18 bits, supports all popular formats including  $I^2S$ .

The 8-bit microcontroller interface gives access to control and status registers. A set of maskable interrupts are available for critical status and error indication.

An external 256K x 4 (or 1M x 4) DRAM can be optionally used for up to one second of data stream buffering. This is also used to enhance error concealment performance and synchronization robustness

April 1996

This is advance information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

| CONTE                                              | NTS                                                                                                                                                                          | Page                             |

|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| I                                                  |                                                                                                                                                                              | 4                                |

| I.1                                                | PIN CONNECTIONS.                                                                                                                                                             | 4                                |

| 1.2                                                | PIN DESCRIPTION.                                                                                                                                                             | 5                                |

| II                                                 | BLOCK DIAGRAM                                                                                                                                                                | 7                                |

| III                                                | FUNCTIONAL DESCRIPSTION.                                                                                                                                                     | 7                                |

| .1<br>   .2<br>   .3<br>   .4                      | STi4500/STi4510 ARCHITECTURE .<br>INPUT FORMATS ACCEPTED .<br>SYSTEM TIME CLOCK .<br>DOCUMENTATION CONVENTIONS .                                                             | 7<br>8<br>9<br>9                 |

| III.5                                              | SUMMARY SPECIFICATION                                                                                                                                                        | 9                                |

| IV<br>IV.1<br>IV.2<br>IV.3<br>IV.4<br>IV.5<br>IV.6 | MICROCONTROLLER INTERFACE AND COMPRESSED DATA INPUT<br>INTERFACE SIGNALS<br>REGISTER ACCESS<br>INTERRUPTS<br>COMPRESSED DATA INPUT<br>INPUT BUFFER LEVEL CONTROL<br>LATENCY. | 10<br>10<br>11<br>11<br>11<br>11 |

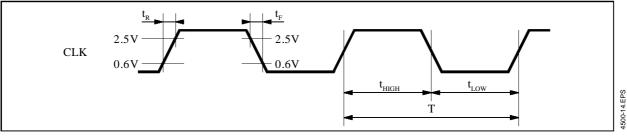

| v                                                  | CLOCKS                                                                                                                                                                       | 12                               |

| V.1                                                | PRIMARY CLOCK                                                                                                                                                                | 12                               |

| V.2<br>V.3                                         | PCM CLOCK. SYSTEM TIME CLOCK                                                                                                                                                 | 12<br>12                         |

| VI                                                 | EXTERNAL DRAM                                                                                                                                                                | 12                               |

| VI.1                                               | GENERAL                                                                                                                                                                      | 12                               |

| VI.2                                               | INTERFACE                                                                                                                                                                    | 13                               |

| VI.3                                               | FRAME DATA STORAGE STRUCTURE AND DELAY                                                                                                                                       | 13                               |

| VII                                                | PCM OUTPUT                                                                                                                                                                   | 13                               |

| VII.1                                              | INTERFACE AND OUTPUT FORMATS                                                                                                                                                 | 13                               |

| VII.2                                              | PCM CLOCK GENERATION                                                                                                                                                         | 14                               |

| VII.3                                              | INTERRUPTS ASSOCIATED WITH PCM OUTPUT                                                                                                                                        | 14                               |

| VIII                                               | DECODER CONTROL                                                                                                                                                              | 15                               |

| VIII.1<br>VIII.2                                   | CONTROL AND STATUS PINS                                                                                                                                                      | 15<br>15                         |

| VIII.3                                             | PLAY AND MUTE                                                                                                                                                                | 15                               |

| VIII.4                                             | RESTART                                                                                                                                                                      | 16                               |

| VIII.5                                             | BITSTREAM SYNCHRONIZATION                                                                                                                                                    | 16                               |

| VIII.5.1<br>VIII.5.2                               | Packet Level Synchronization                                                                                                                                                 | 17<br>18                         |

| VIII.6                                             | ERROR RECOVERY AND CONCEALMENT.                                                                                                                                              | 10                               |

| VIII.7                                             | ANCILLARY DATA EXTRACTION                                                                                                                                                    | 19                               |

| VIII.8                                             | BYPASS MODE                                                                                                                                                                  | 19                               |

# STi4500/STi4510

| CONTENTS (continued)                           |                                                                                                                          |                            |  |  |  |  |

|------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------|--|--|--|--|

| IX                                             | SYSTEM TIME COUNTER                                                                                                      | 20                         |  |  |  |  |

| Х                                              | REGISTER DESCRIPTIONS                                                                                                    | 21                         |  |  |  |  |

| хі                                             | ELECTRICAL SPECIFICATION.                                                                                                | 31                         |  |  |  |  |

| XI.1                                           | ABSOLUTE MAXIMUM RATINGS                                                                                                 | 31                         |  |  |  |  |

| XI.2                                           | DC ELECTRICAL CHARACTERISTICS.                                                                                           | 31                         |  |  |  |  |

| XI.3                                           | AC ELECTRICAL CHARACTERISTICS                                                                                            | 31                         |  |  |  |  |

| XI.3.1<br>XI.3.2<br>XI.3.3<br>XI.3.4<br>XI.3.5 | Primary Clock .<br>DRAM Interface.<br>Microcontroller Interface Timing .<br>Compressed Data Input .<br>PCM Data Output . | 32<br>32<br>37<br>39<br>41 |  |  |  |  |

| XII                                            | PACKAGE MECHANICAL DATA                                                                                                  | 42                         |  |  |  |  |

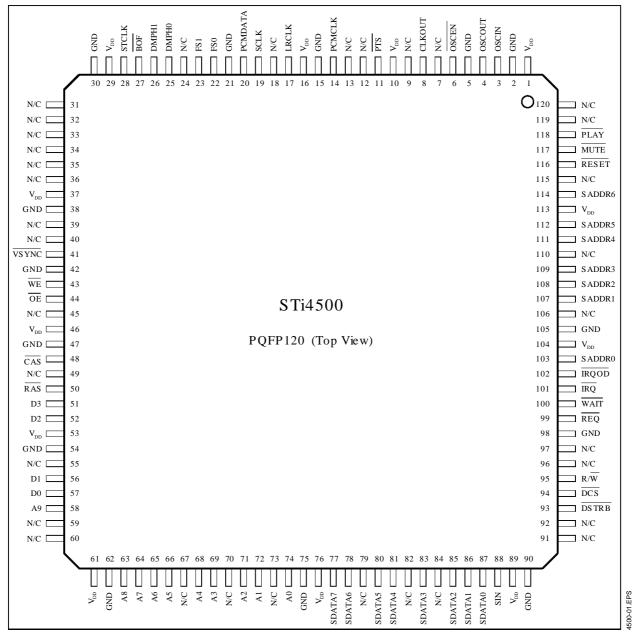

#### **I - PIN INFORMATION**

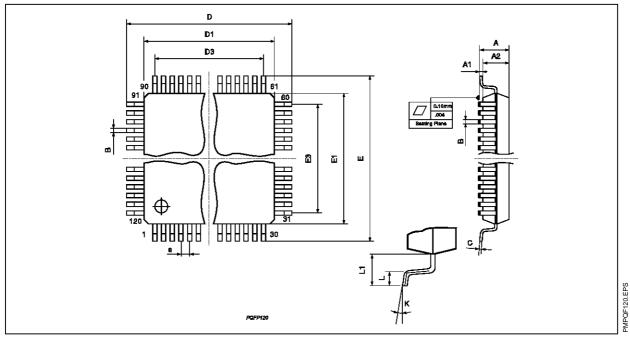

#### I.1 - Pin Connections (STi4500) (PQFP120)

SGS-THOMSON MICROELECTRONICS

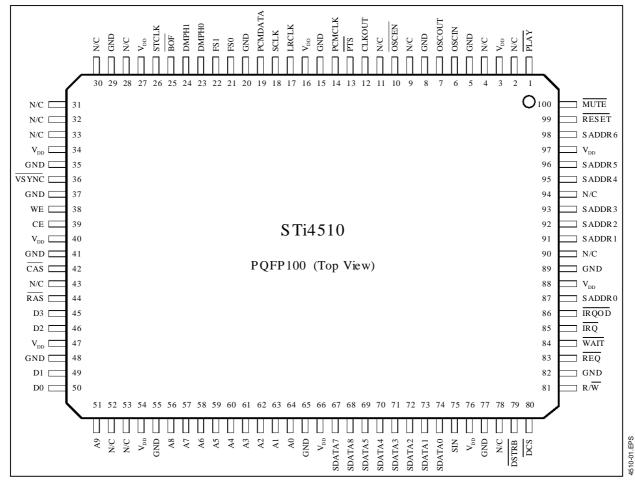

## I - PIN INFORMATION (continued)

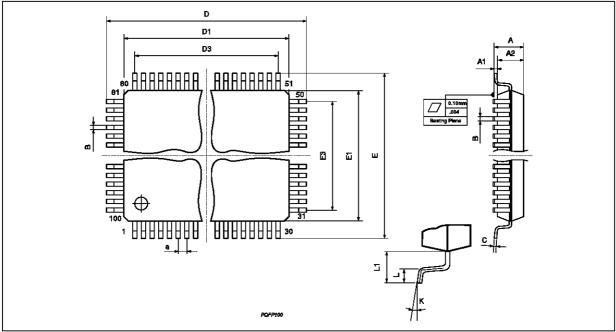

#### I.1 - Pin Connections (STi4510) (PQFP100)

#### **I.2 - Pin Description**

| STi4500                                                                                              | STi4510                                         | Name            | Туре | Function                                               |  |  |  |

|------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------|------|--------------------------------------------------------|--|--|--|

| SYSTEM SERVICES AND NON-FUNCTIONAL PINS                                                              |                                                 |                 |      |                                                        |  |  |  |

| 1,10,16,29,37,46,53,<br>61,76,89,104,113                                                             | 3,12,16,27,34,40,<br>47,54,66,76,88,97          | V <sub>DD</sub> |      | Power Supply                                           |  |  |  |

| 2,5,15,21,30,38,47,<br>54,62,75,90,98,105                                                            | 5,8,15,20,29,35,41,<br>48,55,65,77,82,89        | GND             |      | Ground                                                 |  |  |  |

| 3                                                                                                    | 6                                               | OSCIN           | I    | 24MHz clock input or crystal connection                |  |  |  |

| 4                                                                                                    | 7                                               | OSCOUT          |      | Crystal connection                                     |  |  |  |

| 8                                                                                                    | 11                                              | CLKOUT          | 0    | Buffered 24MHz clock output                            |  |  |  |

| 6                                                                                                    | 9                                               | OSCEN           | In   | Buffered clock output enable                           |  |  |  |

| 116                                                                                                  | 99                                              | RESET           | I    | Master Reset                                           |  |  |  |

| 7,9,12,13,18,24,31-36,39,40,45,<br>49,55,59,60,67,70,73,79,82,84,<br>91,92,96,97,106,110,115,119,120 | 2,4,10,28,30,31,<br>32,33,43,52,53,<br>78,90,94 |                 | N/C  | Reserved pins, leave unconnected, or connect to ground |  |  |  |

| 42                                                                                                   | -                                               |                 | GND  | Reserved pin, connect to ground                        |  |  |  |

4500-01.TBL

# I - PIN INFORMATION (continued)

# I.2 - Pin Description (continued)

| STi4500                     | STi4500 STi4510 Name  |                 | Туре           | Function                               |

|-----------------------------|-----------------------|-----------------|----------------|----------------------------------------|

| DRAM INTERF                 | ACE                   |                 |                |                                        |

| 51,52,56,57                 | 45,46,49,50           | D3 - D0         | I/O            | Bidirectional data port                |

| 58,63-66,68,<br>69,71,72,74 |                       |                 | 0              | Address                                |

| 50                          | 44                    | RAS             | 0              | Row address strobe                     |

| 48                          | 42                    | CAS             | 0              | Column address strobe                  |

| 44                          | 39                    | OE              | 0              | Output enable                          |

| 43                          | 38                    | WE              | 0              | Write enable                           |

| SYSTEM TIME                 | CLOCK CONTR           | OL              |                |                                        |

| 28                          | 26                    | STCLK           | I              | System clock                           |

| 41                          | 36                    | VSYNC           | I              | Video vertical synchronization signal  |

| PCM OUTPUT I                | NTERFACE              | •               |                | •                                      |

| 20                          | 19                    | PCMDATA         | 0              | PCM serial data output                 |

| 14                          | 14                    | PCMCLK          | Ι              | PCM clock input                        |

| 19                          | 18                    | SCLK            | 0              | PCM clock output                       |

| 17                          | 17                    | LRCLK           | 0              | Left/right channel select output       |

| MICROCONTRO                 |                       | ACE             |                | 1                                      |

| 77,78,80,81,<br>83,85-87    | 67-74                 | SDATA7 - SDATA0 | I/O            | Bidirectional data bus                 |

| 114,112,111,<br>109-107,103 | 98,96,95,<br>93-91,87 | SADDR6 - SADDR0 | I              | Address                                |

| 94                          | 80                    | DCS             | I              | Chip select                            |

| 95                          | 81                    | R/W             | I              | Read/write selection                   |

| 100                         | 84                    | WAIT            | O (3-state)    | Data acknowledge                       |

| 101                         | 85                    | ĪRQ             | 0              | Interrupt request                      |

| 102                         | 86                    | IRQOD           | O (open-drain) | Interrupt request, open drain output   |

| COMPRESSED                  | DATA INPUT            |                 |                |                                        |

| 88                          | 75                    | SIN             | I              | Serial compressed data input           |

| 93                          | 79                    | DSTRB           | I              | Compressed data input strobe           |

| 99                          | 83                    | REQ             | 0              | Compressed data request                |

| DECODING CO                 | NTROL AND S           | TATUS           |                | •                                      |

| 118                         | 1                     | PLAY            | I              | Enable output of decoded audio         |

| 117                         | 100                   | MUTE            | I              | Forced muted audio output              |

| 26,25                       | 24,23                 | DMPH1, DMPH0    | 0              | De-emphasis mode of current frame      |

| 23,22                       | 22,21                 | FS1,FS0         | 0              | Sampling frequency of current frame    |

| 27                          | 25                    | BOF             | 0              | Beginning of frame at PCM output       |

| 11                          | 13                    | PTS             | 0              | Frame at PCM output has associated PTS |

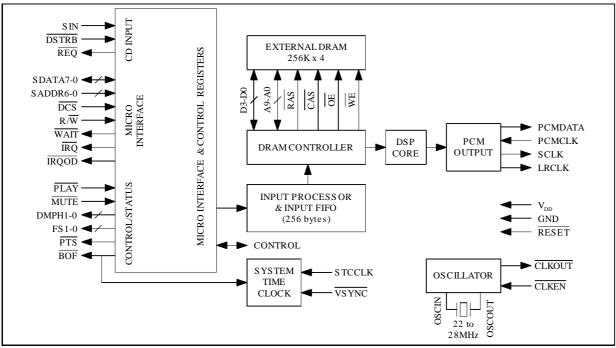

## II - BLOCK DIAGRAM

## Figure 1

## **III - FUNCTIONAL DESCRIPTION**

### III.1 - STi4500/STi4510 Architecture

The STi4500/STi4510 has 5 principal blocks:

- host interface and control registers

- input processor

- DRAM controller

- DSP core

- PCM output

The interconnection of these blocks, and all external interfaces, are shown in Figure 1.

## Host Interface and Control Register

The block implements the 8-bit interface to the host processor. All control registers are accessible through this block.

#### Input Processor

The block is responsible for the parsing of the bitstream at the packet level, implementation of the synchronizing algorithms, decoding of time stamps, and the tagging of the audio bitstream with the appropriate PTS before storage in the DRAM. There is an internal 256-byte FIFO buffer.

#### **DRAM Controller**

This block has the functions of testing for the presence of DRAM and generating of all necessary DRAM control signals.

#### DSP Core

This block performs bitstream decoding and synthesis subband filter execution, according to layers I and II of the MPEG algorithm.

#### PCM Output

This block organises the PCM audio output into the required serial format, and generates all of the D-A converter control signals. In addition, a system time clock counter is provided, which is not directly connected to any of the above blocks. This function is required when managing synchronization in an audio/video decoding system.

1500-02.EPS

#### **III - FUNCTIONAL DESCRIPTION** (continued)

#### **III.2 - Input Formats Accepted**

The STi4500/4510 is able to accept the following 3 types of bitstream :

- MPEG audio elementary stream, as defined by ISO/IEC 11172-3, Layers I and II

- ISO/IEC 11172-1 packets with syntax as shown below

no. of bits packet() { 24 packet\_start\_code\_prefix stream\_id 8 16 packet\_length if(stream\_id != private\_stream\_2) { while (nextbits() == '1111 1111') stuffing\_byte 8 if (nextbits() == ' 01') { ·01' 2 STD buffer scale 1 13 STD\_buffer\_size } if (nextbits() == '0010') { '0010' Δ presentation\_time\_stamp[32..30] 3 marker\_bit presentation\_time\_stamp[29..15] 15 marker bit presentation\_time\_stamp[14..0] 15 marker\_bit 1 } else if (nextbits() == '0011') { '0011<sup>'</sup> presentation\_time\_stamp[32..30] 3 marker\_bit presentation\_time\_stamp[29..15] 15 marker\_bit presentation\_time\_stamp[14..0] 15 marker\_bit 1 **'0001**' decoding\_time\_stamp[32..30] 3 marker\_bit decoding\_time\_stamp[29..15] 15 marker\_bit decoding\_time\_stamp[14..0] 15 marker\_bit else '0000 1111' 8 for (i=0; i N; i++) { packet\_data\_byte 8

} }

The outlined parts indicate the information which is extracted by the STi4500/4510. The other items of packet body information are ignored.

- uncompressed PCM data (for bypass mode)

## III - FUNCTIONAL DESCRIPTION (continued)

#### III.3 - System Time Clock

This function is included to assist the implementation of audio/video synchronization in decoding systems.

The system time clock (STC) counter is incremented by a '90 kHz' programmable sub-multiple of the input STCCLK, which could be, for example be fed from the same clock as PCMCLK. The value of STC can be latched by both BOF (internal signal indicating beginning of audio frame), and VSYNC (externally provided video picture synchronization signal), and read by the host controller.

#### **III.4 - Documentation Conventions**

In this data sheet, the following conventions are used when documenting the functions of signals :

I/O signals can either be **active high** or **active low**. The former have names without an overbar (i.e. <u>SIGNAL</u>), the latter have an overbar (i.e. SIGNAL). Where a signal has two different and mutually exclusive actions, a dual name is used (e.g. COME/GO).

Internal signals and variable names (e.g. bits in registers) are always documented as active high.

When the condition indicated by the name of the signal or variable is **true**, the signal or variable is said to be true, **asserted** or to have the value 1.

When the condition indicated by the name of the signal or variable is not true, the signal or variable is said to be **false**, **de-asserted** or to have the value 0.

When an active high signal is true or asserted, the logic voltage level is high.

When an active low signal is true or asserted, the logic voltage level is low.

When an internal signal or variable is **set**, it has the value 1. A bit is never "set to 0", but "reset to 0".

When an internal signal or variable is  $\ensuremath{\textit{reset}}$  , it has the value 0.

Hexadecimal numbers are indicated by appending an "h", e.g. A70h.

#### **III.5 - Summary Specification**

#### Bitstreams accepted

ISO/IEC 11172-3 audio elementary stream ISO/IEC 11172-1 packets Audio PCM data (for decoder bypass)

#### Performance

ISO/IEC 11172-3 Layers I & II All MPEG input bitrates supported with sampling rates of 32, 44.1 and 48kHz, free format at 32 & 48kHz sampling rates

Decodes in single channel, dual channel, stereo, or joint stereo modes

#### System Clock

24MHz nominal

#### Microcontroller Interface

8-bit interface with "wait" signal handshake. Interrupt request signal. Dedicated control inputs for "play" and "mute".

#### Compressed Data Input

Bit or byte-mode input Burst rate up to 20 Mbit/s

#### External DRAM

External 1Mbit DRAM option for audio delay and error concealment by frame repeat Standard interface for 256K X 4 or 1M X 4 DRAM

#### PCM Output

16 or 18-pit PCM output I<sup>2</sup>S and other popular formats supported

#### System Time Clock and Support for A/V Sync

Host-accessible counter included for handling of audio/video synchronization. Sampled on start of audio frame or video picture output. PTS extraction from MPEG packet layer.

#### Error Concealment

Automatic error concealment on CRC or synchronization error detection

#### Package

120-pin PQFP or 100-pin PQFP

# Power Consumption

425mW typical

#### IV - MICROCONTROLLER INTERFACE AND COMPRESSED DATA INPUT

#### IV.1 - Interface Signals

The combined microcontroller/compressed data interface consists of the following signals :

- SDATA7 - SDATA0 : I/O data port - SADDR6-SADDR0 : I address - R/W : 1 read/write selection - DCS :1 register read/write strobe - WAIT : 0 acknowledge - SIN : 1 serial CD input - DSTRB :1 CD write strobe - REQ : O CD data request - IRQ, IRQOD : O Interrupt request

Input of compressed data in byte mode and read/write access to ST4500/4510 control registers share the same 8-bit data port, SDATA7-SDATA0. The signal DCS requests a register access cycle, while the signal DSTRB requests a compressed data write cycle. R/W selects the direction of transfer for a register access. Register addresses are selected by the 7 address bits SADDR6-SADDR0.

If compressed data is input in byte mode, the multiplexing of compressed data and control bytes on to SDATA7-SDATA0, as well as arbitration of compressed data and register read/write cycles, must be performed externally.

Compressed data can also be input in serial mode through the dedicated port SIN.

WAIT (a 3-state output) is the acknowledge for register access cycles triggered by DCS. REQ indicates that the STi4500/4510 is available for the input of compressed data, and together with DSTRB, makes a DMA handshake.

Interrupt requests are signalled by IRQ. An alternative open-drain interrupt request, IRQOD, is also provided.

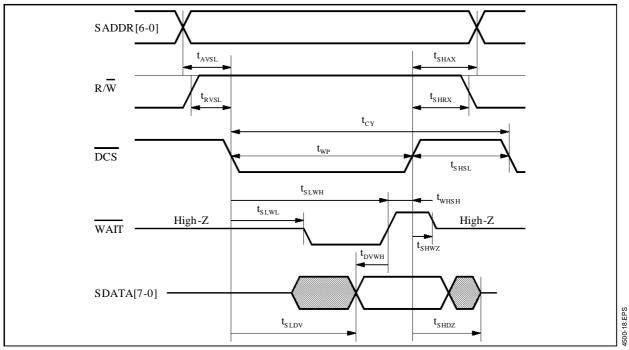

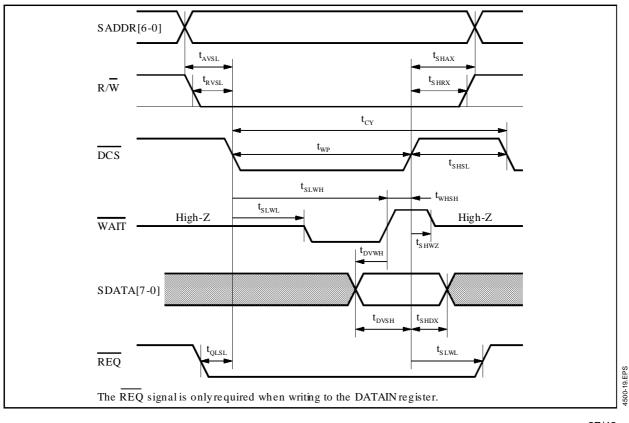

#### IV.2 - Register Access

The address bits, SADDR6-SADDR0, select one of the 128 one-byte control register locations. The function of each register is detailed in section 8.0, "REGISTER DESCRIPTIONS". Some are read/write, some read-only, and some write-only. The signal R/W defines whether the register access is a read or a write (high for read, low for write).

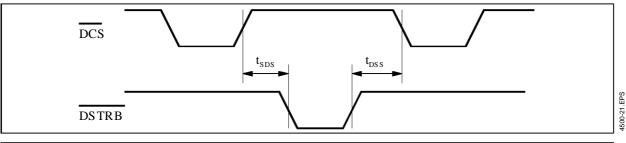

A cycle is defined by the assertion of signal  $\overline{\text{DCS}}$ . In response to this the signal WAIT is always asserted. The address, read/write and data inputs must be set up before DCS line is activated.

If a read cycle is requested, the data lines SDATA7-SDATA0 will be driven by the STi4500/4510. For a write cycle the STi4500/4510 will latch the <u>data placed</u> on the data lines on the rising edge of DCS.

When WAIT is de-asserted, indicating the completion of the read or write operation, DCS can return to its high state and the cycle ends. The timing of register read/write cycles is given in Figure 16 and Figure 16 of section 9.3.3, "Microcontroller Interface Timing". The minimum time between two successive read or write cycles is 100 ns. The signal WAIT is in its high state when a read/write cycle is not in progress (i.e. while DCS is high).

During a register read/write cycle (i.e. while  $\overline{DCS}$  is low), the compressed data input strobe DSTRB must be high if :

- 1. The STi4500/4510 is configured for byte-mode compressed data input (i.e register SIN\_EN = 0),

- 2. The STi4500/4510 is configured for serial compressed data input (i.e. register SIN\_EN = 1), and register DATAIN is being accessed.

The relative timing constraints of these two signals are given in Figure 18 of section XI.3.3, "Microcontroller Interface Timing".

## IV - MICROCONTROLLER INTERFACE AND COMPRESSED DATA INPUT (continued)

#### IV.3 - Interrupts

The conditions that can cause an interrupt are listed in the table below :

| No | Condition Signalled                  |

|----|--------------------------------------|

| 14 | First bit of new frame at PCM output |

| 13 | Input FIFO full                      |

| 12 | Input FIFO level = FIFO_THRES        |

| 11 | External DRAM full                   |

| 10 | De-emphasis changed                  |

| 9  | Sampling frequency changed           |

| 8  | PCM output buffer underflow          |

| 7  | Ancillary data register full         |

| 6  | not used                             |

| 5  | CRC error detected                   |

| 4  | Blocks in DRAM $\geq$ BALF_LIM       |

| 3  | Blocks in DRAM $\leq$ BALE_LIM       |

| 2  | Valid PTS registered                 |

| 1  | Valid header registered              |

| 0  | Change in synchronization status     |

An interrupt is enabled by setting the corresponding bit in the interrupt mask register, INTR\_EN. An interrupt is signalled externally by a 100 ns pulse appearing on IRQ. At the same time one of the bits of the interrupt register, INTR, becomes set. The interrupt source may then be identified by reading INTR.

The most significant byte (bits 8-14), and bits 3-5 of the least significant byte of INTR can be independently cleared by reading. Bits 0-2 and 7 are cleared by a different method, as explained in the description of the INTR register in section X, "REG-ISTER DESCRIPTIONS". If the condition giving rise to the interrupt remains, a new interrupt will be generated.

The INTR and INTR<u>EN registers are cleared on</u> reset (assertion of RESET pin or writing to the RESET register), or restart (writing to the RE-START register).

#### **IV.4 - Compressed Data Input**

The following 3 types of bitstream may be input :

- 1. MPEG audio elementary stream, as defined by ISO/IEC 11172-3, Layers I and II.

- 2. ISO/IEC 11172-1 packets.

- 3. uncompressed PCM data.

The input mode is determined by the programming of register STR\_SEL (see section X, "REGISTER DESCRIPTIONS").

There are three possible ways of inputting compressed data, shown in the table below :

|                  | Serial Input<br>(SIN_EN = 1) | Parallel Input<br>(SIN_EN = 0) |

|------------------|------------------------------|--------------------------------|

| Strobed by DSTRB | DMA mode                     | DMA mode                       |

| Strobed by DCS   |                              | Write to DATAIN                |

The compressed bit stream can be input in parallel or serial mode depending on the value of SIN\_EN register.

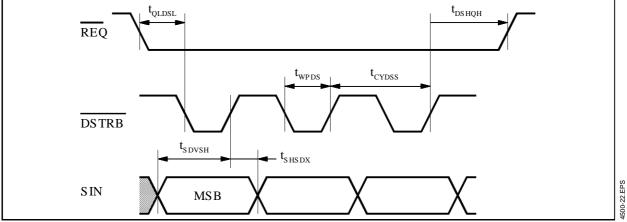

If serial mode is selected, data is placed on <u>pin SIN</u>, and strobed in <u>on</u> the rising edge of signal DSTRB. If the signal REQ is <u>asserted</u> (low), then another data bit can be input. REQ goes high when the input buffer is full. Two further bits can safely be entered after this. Serial input timing is given in Figure 20 of section XI.3.4, "Compressed Data Input".

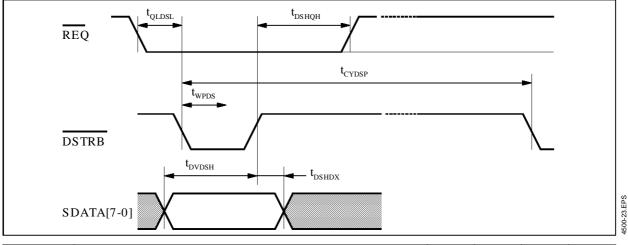

If parallel mode is selected, data can be input using DSTRB as described <u>above</u>, or by writing to the DATAIN register using DCS. If the signal REQ is <u>asserted</u> (low), then another data byte can be input. REQ goes high when the input buffer is full. ONE further byte can safely be entered after this. Parallel input timing is given in Figure 20 of section XI.3.4, "Compressed Data Input" and Figure 16 of section XI.3.3, "Microcontroller Interface Timing".

The signal  $\overline{\text{REQ}}$  is high for the duration of the reset and restart processes (see section VIII.2, "Initialization of the Decoder" and section VIII.3, "Play and Mute" ).

The relative timing constraints between DCS and DSTRB specified in section IV.2, "Register Access", must be respected.

Data may be input in bursts at rates of up to 20 Mbit/s in serial mode, or 2.5 Mbyte/s in parallel mode.

## IV.5 - Input Buffer Level Control

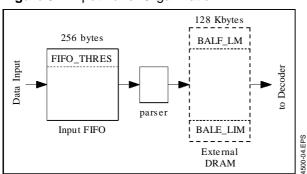

The input buffering is shown in Figure 2. Input data is entered into a 256-byte FIFO store before interpretation by the parser. If external DRAM is installed, and low latency mode (LATENCY = 0) or bypass mode (STR\_SEL =  $11_2$ ) are not enabled, audio frames are stored in an additional 128 Kbyte buffer before being sent to the decoder. The format of data storage in the DRAM buffer is given in section VI.3, "Frame Data Storage Structure and Delay".

5 interrupts are available for the monitoring of buffer levels, two relating to the input FIFO, and three relating to the DRAM buffer.

#### IV - MICROCONTROLLER INTERFACE AND COMPRESSED DATA INPUT (continued)

Interrupt 13 indicates that the input FIFO is full, while interrupt 12 indicates that the input FIFO level is equal to the value loaded into register FIFO\_THRES. Interrupt 12 is generated whenever the level crosses the threshold. It is recommended to use REQ to control input data flow whenever possible.

The level of data in the DRAM buffer can be read from register BUFF\_LEVEL. Two thresholds can be set: an upper level in BALF\_LIM, and a lower one in BALE\_LIM. When the level is greater than BALF\_LIM, interrupt 4 is generated, when it is lower than BALE\_LIM, interrupt 3 is generated. When the DRAM buffer is full, interrupt 11 is generated.

All buffers are flushed after a reset or restart.

#### Figure 3 : Input Buffer Organization

#### IV.6 - Latency

Before being able to output samples, the STi4500/4510 must first be synchronized to the bitstream. After this the decoder requires a certain amount of data, equal to roughly 1/12 of a frame, before the output samples can be computed. The time required to compute these samples is about 2ms.

The total delay is equal to the sum of the synchronization time, the time required to input the data, and the decoding time. The synchronization time is time required to skip zero, one, two or three frames (see section VIII.5, "Bitstream Synchronization"). This depends on the Layer and sampling frequency, and has a maximum value of  $3 \times 36 = 108$ ms (frame Duration for Layer II at 32kHz). Similarly, the longest data input time is 36/12 = 3ms. Once the STi4500/4510 is synchronized, the longest latency in low latency mode is 3 + 2 = 5ms.

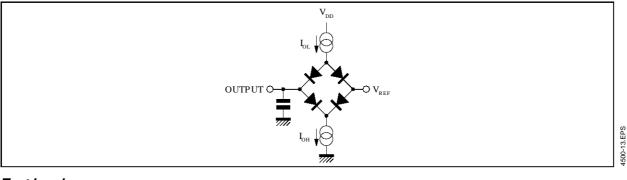

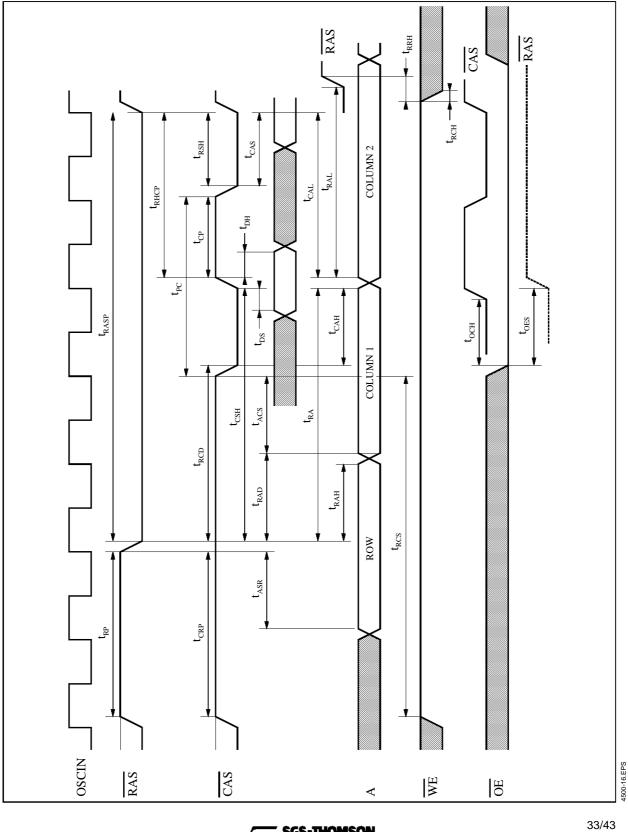

## V - CLOCKS V.1 - Primary Clock

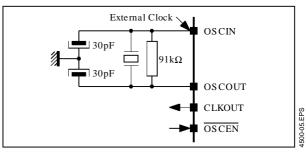

The STi4500/4510 primary clock, which has a nominal value of 24MHz, can either be independently generated or derived from another system clock. It can either be input directly on Pin OSCIN, or generated from a crystal using the circuit shown in Figure 4.

The crystal should be a fundamental-mode, parallel-resonant, 15pF device. The values of the capacitors shown should be in the range of 10 to 30pF.

## V.2 - PCM Clock

The input PCMCLK is used to generate the PCM output bit clock. Programming of the internal clock divider is described in section VII.2, "PCM Clock Generation".

## V.3 - System Time Clock

The input STCLK is used to generated the system time clock, which is used to increment the system time clock counter. Programming of the internal clock divider is described in section IX, "SYSTEM TIME COUNTER".

## VI - EXTERNAL DRAM

## VI.1 - General

The utilisation of an external 1 Mbit DRAM provides the following capabilities :

- At least one second of audio may be buffered for the purposes of audio/video synchronization

- Error concealment by frame repeat

- Skip and repeat of audio frames

- Synchronization look-ahead

The STi4500/4510 is designed to interface with a (120ns maximum) 256K x 4 DRAM. It is also designed to support a  $1M \times 4$  DRAM in the event that the  $1M \times 4$  DRAM becomes less expensive than the 256K x 4. When a  $1M \times 4$  DRAM is used, only 256K x 4 of the1M x 4 is utilised.

## VI - EXTERNAL DRAM (continued)

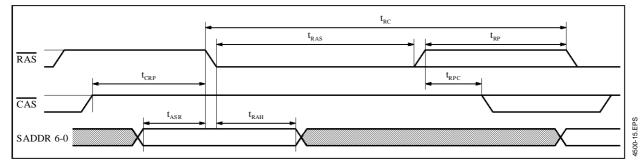

#### VI.2 - Interface

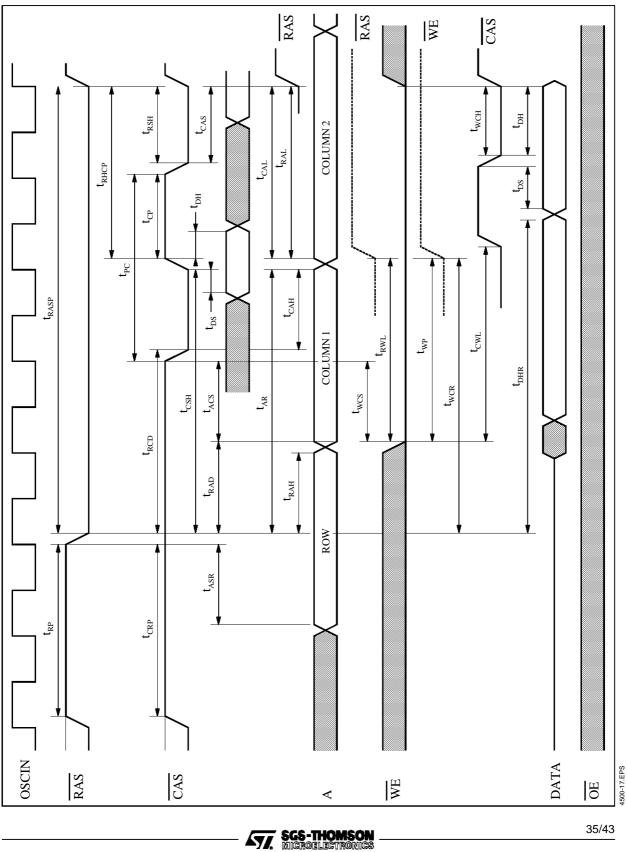

The memory interface contains the following signals :

- D3 D0 bidirectional data port

- A9 A0 address

- RAS row address strobe

- CAS column address strobe - OE output enable

- OE output enable - WE write enable

Memory timing diagrams are shown in section XI.3.2, "DRAM Interface".

The STi4500/4510 provides a 655µs power-on pause followed by 16 initialization cycles.

At power-up, the bit DRAM\_EXT is set automatically to indicate whether an external DRAM is connected.

#### VI.3 - Frame Data Storage Structure and Delay

Frame data is stored in the external DRAM in units of blocks, each containing 1024 bytes. The maximum number of blocks which can be stored in the 1 Mbit memory is 128.

A Layer I audio frame is always stored in one block. A Layer II audio frame is always stored in two blocks.

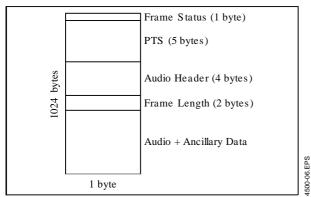

The organisation of data within a block is shown in Figure 5.

The first byte is a status word indicating whether or not the frame is valid. After this, a second byte indicates whether the following PTS code is valid. The PTS value is stored in 5 bytes. After the PTS, the 4-byte audio frame header is stored. Following the header is the frame length (2 bytes). Finally the compressed audio data, plus any ancillary data, is stored.

#### Figure 5 : DRAM Block Format

The amount of audio delay possible in 128 blocks depends on the layer and sampling rate.

For layer I : delay = (384 X 128) / sampling rate For Layer II : delay = (1152 X 64) / sampling rate The table below gives the values possible.

|          | Sampling Frequency |         |         |  |  |

|----------|--------------------|---------|---------|--|--|

|          | 32kHz              | 48kHz   |         |  |  |

| Layer I  | 1.536 s            | 1.115 s | 1.024 s |  |  |

| Layer II | 2.304 s            | 1.672 s | 1.536 s |  |  |

#### VII - PCM OUTPUT VII.1 - Interface and Output Formats

The decoded audio data is output in serial PCM format. The interface consists of the following signals :

- PCMDATA PCM serial data output

- SCLK PCM clock output

- LRCLK Left/right channel select output

- PCMCLK PCM clock input

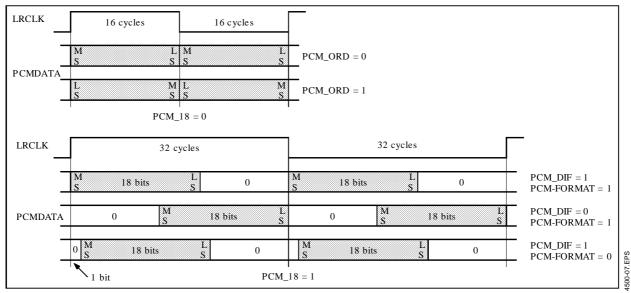

Output precision is selectable to be either 16 bits/word or 18 bits/word by setting the output precision select, PCM\_18, register.

In 16-bit mode, data may be output either with the most significant bit first or least significant bit first as selected by the contents of the output order select, PCM\_ORD, register.

When 18-bit data is selected, 32 bits are output for each channel. The data in front register, PCM\_DIF, is used to position the 18 data bits either at the beginning or at the end of each 32-bit frame. The PCM\_FORMAT register is used to select standard or  $I^2S$ -compatible format when 18-bit precision is selected.

Figure 6 shows the five different output formats which are possible. PCM\_ORD only has significance in 16-bit mode. PCM\_DIF only has significance in 18-bit mode. PCM\_FORMAT only has significance in 18-bit mode and when PCM\_DIF = 1. The last option shown in Figure 6 is compatible with the  $I^2S$  format.

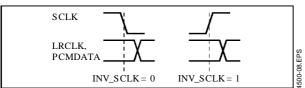

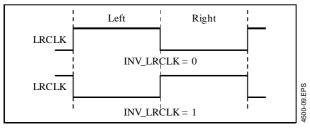

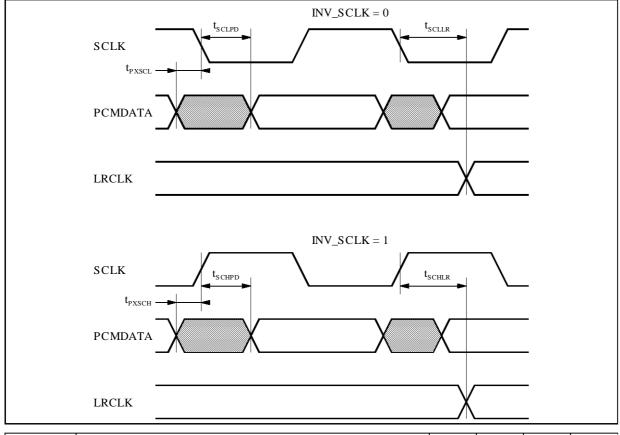

The polarity of the PCM serial output clock, SCLK, and the left/right channel selection, LRCLK, are selected by bits INV\_SCLK and INV\_LRCLK, respectively.

Figure 7 shows the two polarities of SCLK. Normally, the DAC will sample LRCLK and PCMDATA on the rising edge of SCLK in the first case, and on the falling edge of SCLK in the second. The first option (INV\_SCLK = 0) is the one normally used in  $I^2S$  systems.

Figure 8 shows how the polarity of LRCLK is selected. The second option (INV\_LRCLK = 1) is compatible with the  $I^2S$  format.

PCM interface timing is given in Figure 20 of section XI.3.4, "Compressed Data Input".

## VII - PCM OUTPUT (continued)

Figure 6 : PCM Output Formats

SGS-THOMSON

Figure 7 : SCLK Polarity

Figure 8 : LRCLK Polarity

## VII.2 - PCM Clock Generation

The PCM serial clock SCLK is derived from the clock input PCMCLK. The frequency of PCMCLK may be equal to the PCM output bit rate, or it may be an integer multiple of this, allowing the use of oversampling D-A converters. In many applications PCMCLK is externally synchronized to the compressed audio bit stream.

SCLK is derived from PCMCLK by dividing it by the contents of the divider register, PCM\_DIV.This number, in the range 0 to 63, defines the ratio of the frequency of the PCM bit clock, SCLK, to that of PCMCLK, according to the relationship :

$$f_{SCLK} = \frac{f_{PCMCLK}}{2 \cdot (PCM DIV + T)}$$

For example, PCM\_DIV is loaded with 0, the frequency of SCLK is one half of the frequency of PCMCLK, while if PCM\_DIV is loaded with 63, the frequency of SCLK is one 128th of the frequency of PCMCLK. The value of PCM\_DIV = 16 is reserved. If this number is loaded, the divider is bypassed and the frequency of SCLK is equal to the frequency of PCMCLK. PCM\_DIV must be set up before the output of SCLK starts. This can be done by first disabling PCM outputs by de-asserting the MUTE and PLAY commands, and then writing to the PCM\_DIV register. Once the register is set up, the MUTE and/or PLAY commands can be asserted. PCM\_DIV cannot be changed "on the fly". The frequency of LRCLK is given by :

$$f_{LRCLK} = \frac{f_{SCLK}}{32}$$

; for 16-bit PCM output

$f_{LRCLK} = \frac{f_{SCLK}}{64}$ ; for 18-bit PCM output

#### VII.3 - Interrupts Associated with PCM Output

There are two interrupts associated with the PCM output, interrupt 8, "PCM Buffer Underflow", and interrupt 14, "Output of New Frame".

An interrupt 8 is generated (if not masked) when a new output sample is required and the PCM buffer is empty. The PCM buffer, which contains up to 64 samples (i.e. 64 word-pairs in stereo), receives the decoded outputs from the DSP core. If the buffer is empty the output sample will have the value zero. Decoding will not stop. If the PCM buffer becomes full, decoding will stop, but PCM output will not be affected.

An interrupt 14 is generated (if not masked) whenever the first bit of a frame appears at the PCM output.

## VIII - DECODER CONTROL

### VIII.1 - Control and Status Pins

MUTE forces the output of muted PCM data. PCM muting will be in effect if either this line or the MUTE register is set. Muting does not affect the audio decoding process.

PLAY enables the output of decoded audio data. Output of decoded audio data is enabled only if both this line is asserted and the PLAY register is set. It does not affect the output of muted audio.

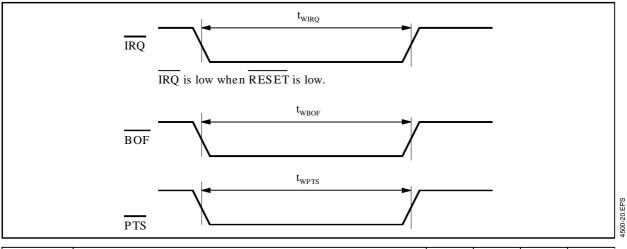

PTS becomes active when the first data word associated with a frame that contained a PTS (presentation time stamp) is at the PCM output stage. PTS is active for a duration of 1ms. The PTS associated with the current frame may be read from PTS[32:0]. This register is updated only if its associated interrupt request is enabled.

The falling edge of  $\overline{\text{BOF}}$  signals the beginning of a new audio frame. The first sample of the new frame is on the PCM output at the falling edge of this signal. This signal is active for a duration of 180ns.

FS1, FS0 signal the sampling frequency code extracted from the frame header. This data is also available in the PCM\_FS register. The FS1 and FS0 pins will reflect the current sampling frequency when the first data point is at the PCM output stage. If enabled, an interrupt 9 is generated at this time if the sampling frequency value has changed.

DMPH1, DMPH0 signal the audio de-emphasis code extracted from the frame header. The same information is also available in the DMPH register. If enabled, an interrupt 10 is generated on a change in the DMPH value. The interrupt occurs and the DMPH1 and DMPH0 pins change state when the corresponding frame is at the PCM output stage.

The action of RESET is described in the following section.

#### VIII.2 - Initialization of the Decoder

There are two methods of initiating a reset of the STi4500/4510:

- 1. Writing 0 or 1 (after which it is automatically restored to the <u>0 state</u>) to the register RESET.

- 2. Asserting the RESET pin for a duration of at least 200ns.

Either of these actions will reset the INTR and INTR\_EN registers. In addition, asserting the RE-SET Pin will reset the registers INV\_SCLK, MUTE, PLAY, STC\_INC and STC\_CTL. All other registers must be set up by the microcontroller before decoding is started.

A reset, initiated either by RESET Pin or by register write initiates the following actions :

- The <u>RESET</u> register is set (if not set already).

- The REQ Pin goes high.

- The INTR, INTR\_EN and BUFF\_LEV registers are reset.

- The registers INV\_SCLK, STC\_INC, STC\_DIV and STC\_CTL are cleared (only if reset was activated by RESET Pin).

- The STi4500/4510 checks for the presence of external DRAM and fixes state of bit DRAM\_EXT accordingly.

- The DRAM goes through its power-up refr<u>esh</u> <u>cycling</u> (only if reset was activated by RE-SET Pin).

- All data buffers are cleared. This takes multiple clock cycles.

- The MUTE and PLAY <u>registers</u> are reset (only if reset was activated by RESET Pin). This inhibits the output clocks, LRCLK and SCLK, and places PCMDATA in their inactive state.

- All other control registers remain at their pre-existing state

- The STi4500/4510 terminates the res<u>et cycle</u>. The RESET register is cleared, and the REQ Pin goes low. The PCM output clocks and data remain inactive.

Register accesses by the host interface are not dis<u>abled</u> during the reset process. However, while the REQ Pin is asserted audio data cannot be input.

<u>The  $\overline{IRQ}$  and  $\overline{IRQOD}$  outputs are low while the RESET Pin is asserted.</u>

Changing of layer or sampling frequency requires a prior reset of the decoder.

#### VIII.3 - Play and Mute

Once initialized and configured, decoding and output of PCM data is controlled by the commands PLAY and MUTE.

The command PLAY is asserted when both the PLAY register is set and the PLAY Pin is asserted.

The command MUT<u>E is a</u>sserted if either the MUTE register or the MUTE Pin is asserted.

The actions of the PLAY and MUTE commands are specified in the Table 1.

Table 1 : Mute and Play Functions

| Mute        | Play        | Function                                                                                                                                                                                                                                                                         |

|-------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| de-asserted | de-asserted | No output or decoding.<br>SCLOCK, LRCLK, PCMDATA all move into their inactive state. LRCLK completes its current cycle and stops, SCLK completes its last cycle in the second LRCLK frame and stops.<br>Decoding stops when all internal buffers become full.                    |

| de-asserted | asserted    | Normal decoding and PCM output.<br>When PLAY is re-asserted, PCMDATA resumes where it left off without data loss.                                                                                                                                                                |

| asserted    | de-asserted | PCM clocks only, no decoding.<br>PCMDATA becomes low after the output of the last complete sample. LRCLK and SCLK<br>are not stopped.<br>Decoding stops when all internal buffers become full.<br>When PLAY is re-asserted, PCMDATA resumes where it left off without data loss. |

| asserted    | asserted    | Decoding and muted output (soft mute).<br>PCMDATA gradually decays to zero.<br>Decoding continues normally. Data consumed as if output were playing.                                                                                                                             |

#### VIII.4 - Restart

The restart procedure is invoked when it is required to flush all buffers and restart decoding immediately.

Restart is initiated by writing 0 or 1 (after which it is automatically restored to the 0 state) to the RESTART register. A restart initiates the following actions :

- The REQ Pin goes high

- The INTR and INT\_EN registers are cleared.

- The BUFF\_LEV register is cleared.

- All data buffers are cleared.

- The MUTE, PLAY and all others registers (except those mentioned above) remain in their existing state.

- Registers access is not disabled. However, while the REQ Pin is high audio data cannot be input.

- The STi4500/4510 terminates the restart cycle. The RESTART register is cleared, and the REQ Pin goes low

The DRAM does not go through the power-up refresh cycle during the restart sequence.

#### VIII.5 - Bitstream Synchronization

The compressed input bit stream must be synchronized before the decompression step may begin. This is done by looking for synchronization words inserted into the data stream at encoding. Synchronization must be done both at the audio frame and at the system packet layer if present.

At the packet level, the audio decoder will look for a valid start code, doing a bit by bit search. Once an audio packet is found, it extracts the presentation time stamp (PTS), if present, and starts the audio synchronization described below.

At the audio frame level, there is a non-unique sync word at the beginning of the header. The STi4500/4510 attempts to find this sync word by doing a bit by bit search. When found the action taken depends on the contents of the SYNC\_LOCK and LATENCY registers.

VIII.5.1 - Packet Level Synchronization

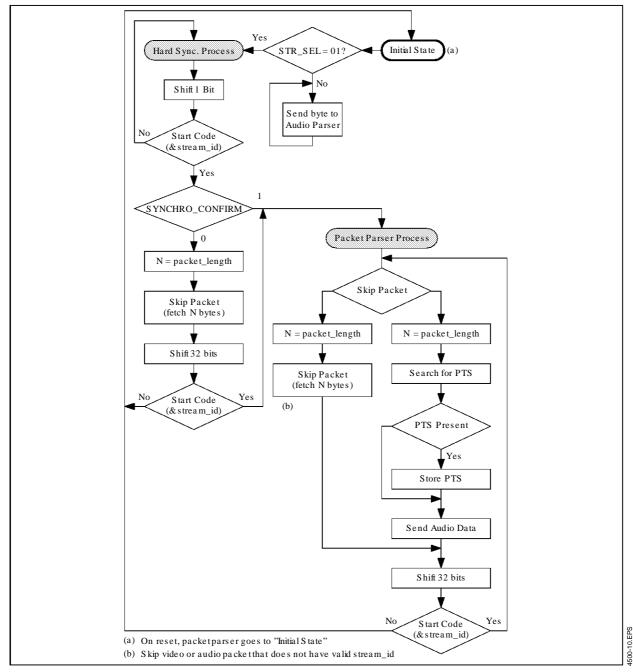

The complete algorithm is given in Figure 9.

Figure 9 : Packet Synchronization Algorithm

To help the synchronization algorithm ignore an emulated packet synchronization word, an extension of the packet start code to be matched is possible. Depending to the content of registers PACKET\_SYNC, AUDIO\_ID and AUDIO\_ID\_EN, synchronization can be made on the 24-bit *packet\_start\_code\_prefix* or can be extended to the *stream\_id* field.

Synchronization mode depends on the type of packets received by the STi4500/4510. The decoder can receive either :

1. Multiplexed audio/video bitstream

(PACKET\_SYNC = 0).

In this case the STi4500/4510 can receive both video and audio streams multiplexed together. Packet synchronization is possible only on the 24-bit start code. All packets are used by the synchronization algorithm but all non-audio packets and, if AUDIO\_ID\_EN is set, all audio packets which have a *stream\_id* which does not match the AUDIO\_ID register value, are not decoded.

2. Multiplexed audio bitstream (PACKET\_SYNC = 1).

In this case, the STi4500/4510 expects to receive only multiplexed audio streams. Synchronization is performed on 27 bits (24 bits *packet\_start\_code\_prefix* + 3 first bits of *stream\_id*). All packets are used by the synchronization algorithm but if AUDIO\_ID\_EN is set, all audio packets that have a *stream\_id* which does not match the AUDIO\_ID register value are not decoded.

3. Single audio bitstream

(PACKET\_SYNC = 2, AUDIO\_ID\_EN=1). Synchronization is performed on 32 bits. All packets are used by the synchronization algorithm, and all audio packets that have a *stream\_id* which matches the AUDIO\_ID register value are decoded.

The SYNCHRO\_CONFIRM register is also taken into account in the global synchronization algorithm. If SYNCHRO\_CONFIRM = 1, after the first packet synchronization word is found the STi4500/4510 is considered to be synchronized. If SYNCHRO\_CONFIRM = 0, after the first packet synchronization word is found, the STi4500/4510 must read the packet length and confirm synchronization by finding the next synchronization word in the correct position.

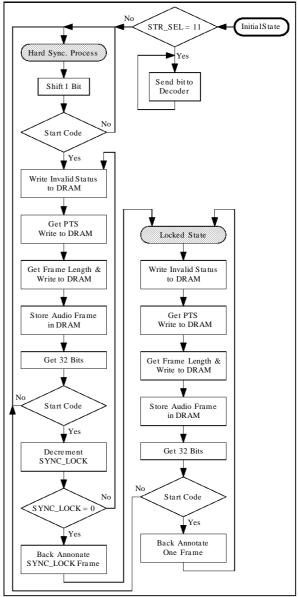

# VIII.5.2 - Audio Frame Synchronization

The synchronization algorithm is given in Figure 10. Because the audio *syncword* can be emulated in the bitstream, it is useful to extend this audio start code to avoid the detection of a false sync word. Each time the STi4500/4510 detects a false sync word during the synchronization process, the delay to reach the locked state increases.

The SYNC\_REG register is used for this purpose. When no field of the SYNC\_REG register is enabled, the STi4500/4510 saves the layer and sampling frequency information after synchronization has been achieved. This aids the task of resynchronization, should synchronization be lost owing to an error in the audio data or the system layer. This internal register is disabled on RESET or RESTART and will not be reinitialized until the audio parser is synchronized.

The SYNC\_LOCK register specifies how many valid synchronization words after the initial one have to be found before entering the locked state. The highest value of SYNC\_LOCK (i.e. 3) is assumed when the SYNC\_REG register has its default value. The definition of a valid synchronization word depends on the LATENCY register value.

Figure 10 : Audio Frame Synchronization Algorithm

In high latency mode (LATENCY = 1) a valid synchronization word is a sequence of bits that matches the expected word. In addition, the calculated length of the audio frame must be equal to the distance to the start of the next sequence of bits matching the synchronization word. In low latency mode (LATENCY = 0), a valid synchronization word is a sequence of bits matching the expected word. High latency mode is not allowed if no DRAM is present.

In free-format mode one additional register (FREE\_FORM) can be used. The FREE\_FORM register is a way of specifying the length of an audio frame in free-format mode. This register is 16 bits long and contains the length of the frame in bits.

The method of storing frames in the DRAM is given in section VI.3, "Frame Data Storage Structure and Delay".

By default a frame is always written always "bad" status. The back annotation process writes a "good" status word. A frame with a "bad" status word is decoded using the concealment method specified by the value of SYNC\_ECM register.

The algorithm without DRAM is similar except that back annotation is not possible. In this case frames are lost before the locked state is achieved.

#### VIII.6 - Error Recovery and Concealment

The STi4500/4510 is able to recover from certain detectable errors. For this purpose it has a number of user-selectable error concealment modes.

Detectable errors may be caused by a bad audio frame CRC or by loss of synchronization. Concealment is similar, but may be selected independently by setting the CRC\_ECM and SYNC\_ECM registers.

The register CRC\_ECM defines the action which will be taken upon detection of a CRC error in an input frame :

- 00 : Disable CRC detection and error concealment

- 01 : Mute on detection of CRC error

- 10 : Repeat last valid frame. Repeat once if Layer II, three times if layer I, mute thereafter. Only possible when external DRAM used.

- 11 : Skip invalid frame

The register SYNC\_ECM defines the action which will be taken upon detection of a synchronization error :

- 00 : Ignore error

- 01 : Mute on detection of synchronization error

- 10 : Repeat last valid frame. Repeat once if Layer II, three times if layer I, mute thereafter. Only possible when external DRAM used.

- 11 : Skip invalid frame

#### VIII.7 - Ancillary Data Extraction

The ancillary data which may be held at the end of audio frames can be extracted and read from the ANC register. This register constitutes a 32-bit FIFO. The first bit of ancillary data received is stored in bit ANC[0].

The extraction of ancillary data in ANC is started by enabling interrupt 7. An interrupt 7 is generated when either :

- 32 bits of ancillary data have been received from the bitstream and written into ANC, i.e. when it is full, or

- 2. the end of a frame is reached.

Register ANC\_AV holds the number of bits available in the ancillary data buffer, ANC[31:0]. When ANC[31:24] is read, interrupt 7 is cleared, ANC\_AV is cleared and the ancillary data buffer is reinitialized. Decoding stops if the STi4500/4510 tries to write data into ANC when it is full. The normal response would be to read ANC\_AV and then ANC. However, if interrupt 7 is disabled (by resetting bit INTR\_EN[7]), decoding will continue and the registers ANC and ANC\_AV will retain their contents until ANC[31:24] is read. If ANC is not read at the end of the frame, and it is not full, ancillary data bits in the next frame will be appended.

#### VIII.8 - Bypass Mode

The STi4500/4510 has an audio bypass capability that allows 16-bit PCM data to be loaded directly and passed through to the PCMDATA output.

To set up audio bypass operation the STR SEL register must be set to the bypass mode (STR\_SEL = 3) and then a reset or restart sequence must be executed. While the REQ output is low, PCM data can be loaded into the device directly. The data is loaded in exactly the same way as compressed data, using one of the three loading mechanisms available. The data can be input at up to the maximum burst rate of 20 Mbit/s. Data must be input in the sequence: 2 bytes left, 2 bytes right, 2 bytes left, and so on. In each byte-pair, the most significant byte must be loaded first. The external DRAM is not used in bypass mode (the LATENCY register must be reset during bypass). All 16-bit PCM output modes can be used in bypass mode. The volume control is operational in bypass mode. The PCM underflow interrupt (interrupt 8) can be used to detect when all bypass data has been output. To switch back to compressed data input, the STR\_SEL register and the LATENCY register must be changed back to select the normal input configuration (STR\_SEL = 0 or 1, LATENCY = 0 or 1) and then a reset or restart sequence must be executed.

#### **IX - SYSTEM TIME COUNTER**

A System Time Counter (STC) has been added to the STi4500/4510 in order to improve integration in a system which includes a video decoder.

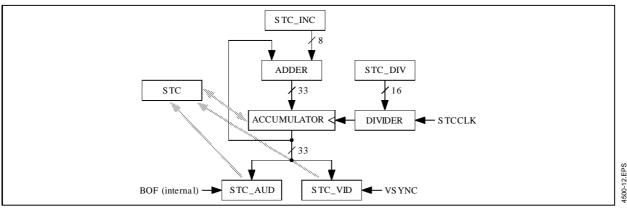

The STC structure is shown in Figure 11. The system time counter itself is constituted by the accumulator and the adder from which its input is taken.

The accumulator clock is derived from an external clock provided by the system (STCCLK), divided by a value programmed into register STC\_DIV. After a reset initiated by assertion of the RE-SET pin, STC\_DIV has the value 0 and STCCLK is not divided. STC\_INC is also reset after assertion of RESET. Connecting PCMCLK to STCCLK allows the STC to be locked to the audio clock.

The accumulator increment is programmable; it is defined by the contents of register STC\_INC. This gives the possibility to use a fractional division of the input clock at the expense of a loss in STC resolution. This is particularly useful when the PCMCLK is used because typical PCMCLK frequencies are not integer multiples of 90kHz.

The STC accumulator will be augmented by STC\_INC every STC\_DIV cycles of STCCLK. If the input clock in M/N times the frequency of the desired STC frequency (usually 90khz), then M is stored in STC\_DIV and N stored in STC\_INC.

The table opposite gives the values of STC\_DIV and STC\_INC for typical values of PCMCLK frequencies.

The lowest STC resolution is that in the first line of the table. The time between STC updates is 45/90000 = 0.5ms.

The register STC\_AUD will latch the STC value at the start of every audio frame (BOF), and the register STC\_VID will latch the STC when the <u>display</u> of very picture display starts (signalled by VSYNC, available through a pin).

The register STC\_CTL is used to transfer data to and from the STC register. Writing to this register with the appropriate bits set will trigger the action. This register is also used to define the polarity of VSYNC. Writing to the register with the appropriate bit set will trigger the defined action. The different functions of the STC\_CTL register are given in the Table 3.

#### Table 2

| Sampling<br>Frequency | PCMCLK<br>Frequency | STC_DIV | STC_INC |

|-----------------------|---------------------|---------|---------|

| 32kHz                 | 8192kHz             | 4096    | 45      |

| 32kHz                 | 12288kHz            | 2048    | 15      |

| 44.1kHz               | 11289.6kHz          | 3136    | 25      |

| 44.1kHz               | 16934.4kHz          | 4704    | 25      |

| 48kHz                 | 12288kHz            | 2048    | 15      |

| 48kHz                 | 18432kHz            | 1024    | 5       |

#### Table 3

| Bit | Function                                 |

|-----|------------------------------------------|

| 7   | Must be low                              |

| 6   | STV_VID latched on rising edge of VSYNC  |

| 5   | STV_VID latched on falling edge of VSYNC |

| 4   | Transfer STC_AUD to STC register         |

| 3   | Transfer STC_VID to STC register         |

| 2   | Transfer STC accumulator to STC register |

| 1   | Transfer STC to accumulator (Mode 1)     |

| 0   | Transfer STC to accumulator (Mode 0)     |

#### Bits 5 and 6 must not be set together.

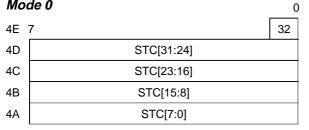

The STC register is a 33-bit value and it is spanned by five 8-bit registers. The "Mode 0" mapping is direct but the "Mode 1" mapping is particular, in which the data are mapped exactly as are the SCR, PTS and DTS values in the bitstream. This mapping avoids bit manipulation when transferring values from the bitstream to the register. The two mappings are defined in the STC register description in section X, "REGISTER DESCRIPTIONS". Mode 0 mapping is applied for read access (STC\_CTL bit 2) and Mode 0 write access (STC\_CTL bit 0).

Mode 1 is applied write access (STC\_CTL bit 1).

Figure 11 : System Time Counter

## **X - REGISTER DESCRIPTIONS**

Registers are listed in alphabetical order. All addresses are in hexadecimal. All unspecified addresses of the register map are reserved, and must not be written to. Unspecified bits of user-accessible registers have no function.

### ANC - Ancillary Data Buffer

| -  | 7 0        |

|----|------------|

| 09 | ANC[31:24] |

| 08 | ANC[23:16] |

| 07 | ANC[15:8]  |

| 06 | ANC[7:0]   |

Address : 09-06 Type : R Reset State : undefined

#### Description

The 4 8-bit ancillary data registers constitute a 32-bit FIFO which holds the ancillary data extracted from audio frames. The first bit of ancillary data received is stored in bit ANC[0].

The extraction of ancillary data in ANC is started by enabling interrupt 7. An interrupt 7 is generated when 32 bits have been written into ANC, i.e. when it is full.

When ANC[31:24] is read, ANC\_AV is cleared and the ancillary data buffer is reinitialized.

#### ANC\_AV - Ancillary Data Available

| 5           |     |   |             | 0 |

|-------------|-----|---|-------------|---|

|             |     |   | ANC_AV[5:0] |   |

| Address     | : 6 | С |             |   |

| Туре        | : F | 2 |             |   |

| Reset State | : 0 |   |             |   |

#### Description

This register holds the number of bits available in the ancillary data buffer, ANC[31:0]. It is cleared by reading ANC[31:24].

#### ATTEN\_L - Left Channel Attenuation

| 5       |              | 0 |

|---------|--------------|---|

|         | ATTEN_L[5:0] |   |

| Address | : 1E         |   |

Iype: R/WReset State: undefined

#### Description

This register defines the left channel attenuation in steps of 2dB. The minimum attenuation is 0dB, the maximum is  $2 \times 63 = 126$ dB.

## ATTEN\_R - Right Channel Attenuation

| 5                              |                              | 0 |

|--------------------------------|------------------------------|---|

|                                | ATTEN_R[5:0]                 |   |

| Address<br>Type<br>Reset State | : 20<br>: R/W<br>: undefined |   |

#### Description

This register defines the right channel attenuation in steps of 2dB. The minimum attenuation is 0dB, the maximum is  $2 \times 63 = 126B$ .

#### AUD\_ID - Audio Stream ID

| 4       |               | 0 |

|---------|---------------|---|

|         | AUD_ID[4:0]   |   |

| Address | : 22<br>· P/M |   |

Iype: R/WReset State: undefined

#### Description

This value stored in this register is only taken into account if AUD\_ID\_EN is set.

This register specifies the number (between 0 and 31) of the audio stream which is to be decoded. The stream number is defined in the field *stream\_id* of the packet header. All other packets will be discarded.

If AUD\_ID\_EN is reset, then all audio packets are decoded.

## AUD\_ID\_EN - Audio Stream ID Enable

|                                | bit 0                        |

|--------------------------------|------------------------------|

|                                | AUD_ID_EN                    |

| Address<br>Type<br>Reset State | : 24<br>: R/W<br>: undefined |

#### Description

If this bit is reset, then the contents of AUD\_ID are ignored.

If it is set, then the register AUD\_ID is taken into account.

- 0 : Ignore AUD\_ID

- 1 : Use AUD\_ID

### BALE\_LIM - Buffer Almost Empty Limit

| 6                              |                              | 0 |

|--------------------------------|------------------------------|---|

|                                | BALE_LIM[6:0]                |   |

| Address<br>Type<br>Reset State | : 69<br>: R/W<br>: undefined |   |

#### Description

This register defines the level of data, in units of blocks, in the external DRAM at or below which an interrupt 3 can be generated.

A block can contain up to 8K bits of data. The external DRAM can contain up to 128 blocks. For Layer I frames, one block is used to store one frame of compressed data. For Layer II frames, two blocks are used to store one frame of compressed data.

#### BALF\_LIM - Buffer Almost Full Limit

| 6       |               | 0 |

|---------|---------------|---|

|         | BALF_LIM[6:0] |   |

| Address | : 6B          |   |

Type : R/W Reset State : undefined

#### Description

This register defines the level of data, in units of blocks, in the external DRAM at or above which an interrupt 4 can be generated.

A block can contain up to 8K bits of data. The external DRAM can contain up to 128 blocks. For Layer I frames, one block is used to store one frame of compressed data. For Layer II frames, two blocks are used to store one frame of compressed data.

#### BUFF\_LEV - DRAM Buffer Level

|    |   | 6 0            |

|----|---|----------------|

| 13 | 7 | BUFF_LEV[14:8] |

| 12 |   | BUFF_LEV[7:0]  |

|    |   |                |

| Address     | : | 13-12                       |

|-------------|---|-----------------------------|

| Туре        | : | R                           |

| Reset State | 1 | 0. Also cleared on restart. |

#### Description

This register indicates the data level in the external DRAM buffer. BUFF\_LEV[14:8] gives the number of complete blocks. BUFF\_LEV[7:0] gives the remainder, in units of 4 bytes (32 bits). When the DRAM is full, the value of BUFF\_LEV[14:8] is 124, and the value of BUFF\_LEV[7:0] is 0.

A block can contain up to 8K bits of data. The external DRAM can contain up to 128 blocks. For Layer I frames, one block is used to store one frame of compressed data. For Layer II frames, two blocks are used to store one frame of compressed data.

#### CRC\_ECM - CRC Error Concealment Mode

| 1 |   |                        | 0 |

|---|---|------------------------|---|

|   |   | CRC_ECM - CRC[1:0]     |   |

|   | : | 2A<br>R/W<br>undefined |   |

#### Description

This register defines the action which will be taken upon detection of a CRC error in an input frame.

- 00 : Disable CRC detection and error concealment

- 01 : Mute on detection of CRC error

- 10 : Repeat last valid frame. Repeat once if Layer II, three times if layer I, mute thereafter. Only possible when external DRAM used.

- 11 : Skip invalid frame

#### **DATAIN - Compressed Data Input**

| 7                              |                              | 0 |

|--------------------------------|------------------------------|---|

|                                | DATAIN[7:0]                  |   |

| Address<br>Type<br>Reset State | : 18<br>: R/W<br>: undefined |   |

#### Description

This register is provided to allow the transfer of compressed data across the microcontroller interface. When this mode of data entry is used, the signal DSTRB must be inactive.

#### **DMPH - De-Emphasis Mode**

| DMPH[1:0] |  |

|-----------|--|

0

Address : 46 Type : R Reset State : undefined

#### Description

1

This register is set with the value of the emphasis field of the frame currently being decoded.

- 00 : None

- 01 : 50/15µs

- 10 : Reserved value

- 11 : ITU-T J.17

#### DRAM\_EXT - External Memory Status

bit 0

| DRAM_EXT |

|----------|

|----------|

Address : 3E

Type : R

Reset State : see below

#### Description

The value of this bit is determined automatically on power-up.

- 0 : No external DRAM present. Only the internal 256-byte input FIFO buffer is used.

- 1 : External DRAM present. Both this memory and the input FIFO are used.

#### FIFO\_THRES - Input FIFO Threshold

| 7 |                 | 0 |

|---|-----------------|---|

|   | FIFO_THRES[7:0] |   |

|   |                 |   |

| Address     | 1 | 52        |

|-------------|---|-----------|

| Туре        | : | R/W       |

| Reset State | : | undefined |

#### Description

This value loaded into this register defines the input FIFO level at which an interrupt 12 can be generated. The level is defined as a byte address, in the range 0 to 255.

An interrupt can be generated each time the FIFO level is equal to FIFO\_THRES, regardless of whether it was approached from above or below. When external DRAM is installed, interrupt 12 should be masked, since interrupts 3 and 4 would normally be used for buffer level indication.

#### FREE\_FORM - Free-Format Frame Length

|    | 7 0             |

|----|-----------------|

| 15 | FREE_FORM[15:8] |

| 14 | FREE_FORM[7:0]  |

|    |                 |

Address : 15-14

Type : R/W Reset State : undefined

#### Description

When free-format decoding is used (*bitrate\_in-dex* = 0), the frame length, if known, can be loaded into this register, in units of bits. (In free-format, the frame length cannot be determined from bitstream parameters).

The length loaded into FREE\_FORM is used in the internal synchronization algorithm.

If the frame length is not known, FREE\_FORM must be loaded with zero.

#### HEADER - Frame Header

|    | 7 0           |

|----|---------------|

| 61 | HEADER[31:24] |

| 60 | HEADER[23:16] |

| 5F | HEADER[15:8]  |

| 5E | HEADER[7:0]   |

|    |               |

| Address     | : | 61-5E     |

|-------------|---|-----------|

| Туре        | : | R         |

| Reset State | : | undefined |

#### Description

This 32-bit register contains the header of the frame currently being decoded.

This register is updated after interrupt 1 is enabled. An interrupt 1 is generated when a valid header has been received.

The contents are retained until HEADER[31:24] is read.

## **INTR - Interrupt Request Register**

|    |   | 6 0        |

|----|---|------------|

| 1B | 7 | INTR[14:8] |

| 1A |   | INTR[7:0]  |

Address : 1B-1A Type : R

Reset State : 0. Also cleared on restart.

## Description

An interrupt is signalled by a 100ns pulse on  $\overline{IRQ}$  whenever one of the bits of INTR becomes set.

This can only occur if the corresponding bit is set in the INTR\_EN register.

The INTR register is cleared on reset (assertion of RESET Pin or setting of RESET register), or restart (setting the RESTART register).

Also the most significant byte, and bits 3-5 of the least significant byte of INTR can be independently cleared by reading.

Bits 0-2 and 7 are cleared by a different method, as indicated in the notes below the following table.

| No | Condition Signalled                           |

|----|-----------------------------------------------|

| 14 | First bit of new frame at PCM output          |

| 13 | Input FIFO full                               |

| 12 | Input FIFO level = FIFO_THRES                 |

| 11 | External DRAM full                            |

| 10 | De-emphasis changed                           |

| 9  | Sampling frequency changed                    |

| 8  | PCM output buffer underflow                   |

| 7  | Ancillary data register full (see Note 1)     |

| 6  | not used                                      |

| 5  | CRC error detected                            |

| 4  | Blocks in DRAM BALF_LIM                       |

| 3  | Blocks in DRAM BALE_LIM                       |

| 2  | Valid PTS registered (see Note 2)             |

| 1  | Valid header registered (see Note 3)          |

| 0  | Change in synchronization status (see Note 4) |

Notes: 1. ANC[31:24] must be read in order to clear bit INTR[7] and to reinitialize the ancillary data buffer.

- 2. PTS[32] must be read in order to clear bit INTR[2] and to reinitialize the PTS register.

- 3. HEADER[31:24] must be read in order to clear bit INTR[1] and to reinitialize the HEADER register.

- 4. SYNC\_ST must be read in order to clear bit INTR[0] and to reinitialize the SYNC\_ST register.

# INTR\_EN - Interrupt Mask Register

|    |   | 6 0        |

|----|---|------------|

| 1B | 7 | INTR[14:8] |

| 1A |   | INTR[7:0]  |

Address : 1D-1C

Type : R/W Reset State : 0. Also cleared on restart.

#### Description

A one in any bit position of this register will enable the corresponding bit of the INTR register.

In addition, setting certain bits of this register have additional actions, as specified below :

- Setting INTR\_EN[7] enables the reading of ancillary data into ANC

- Setting INTR\_EN[2] enables the updating of the PTS register.

- Setting INTR\_EN[1] enables the updating of the HEADER register.

- Setting INTR\_EN[0] enables the updating of the SYNC\_ST register.

## INV\_LRCLK - LRCLK Polarity

| bit 0     |  |

|-----------|--|

| INV_LRCLK |  |

|           |  |

| Address     | : | 11                                  |

|-------------|---|-------------------------------------|

| Туре        | : | R/W                                 |

| Reset State | : | 0 after assertion of RESET Pin only |

#### Description

This bit is used to define the polarity of the output signal LRCLK.

0 : Left channel when LRCLK = 1

1 : Left channel when LRCLK = 0

#### INV\_SCLK - SCLK Polarity

|         |      | bit 0    |  |

|---------|------|----------|--|

|         |      | INV_SCLK |  |

| Address | · 53 |          |  |

Type : R/W

Reset State : 0 after assertion of RESET Pin only

## Description

This bit defines the polarity of the PCM bit clock output SCLK.

- 0 : The LRCLK and PCMDATA outputs change on the falling edge of SCLK. The external DAC will sample LRCLK and PCMDATA on the rising edge of SCLK.

- 1 : The LRCLK and PCMDATA outputs change on the rising edge of SCLK. The external DAC will sample LRCLK and PCMDATA on the falling edge of SCLK (Figure 7).

### LATENCY - Latency Selection

bit 0